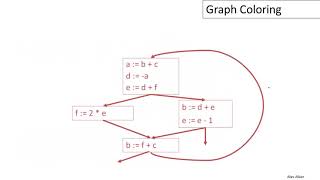

ch 3.41:register allocation by graph coloring |compiler design lectures for gate cse by monalisa cs

Published 3 years ago • 12K plays • Length 11:43Download video MP4

Download video MP3

Similar videos

-

15:13

15:13

ch 3.42:register allocation through labeled expression tree |optimal code generation |ershov numbers

-

18:04

18:04

ch 3.38:register and address descriptors with example | getreg function with spill |compiler design

-

13:46

13:46

ch 3.34:live-variable analysis/liveness analysis example |compiler design lectures for gate cse

-

3:36

3:36

ch 3.21:next-use information | compiler design lecture for gate cse by monalisa pradhan

-

16:26

16:26

ch 3.33:live-variable analysis |liveness analysis |compiler design lectures for gate cse by monalisa

-

55:37

55:37

2018 llvm developers’ meeting: m. braun “register allocation: more than coloring”

-

16:46

16:46

register allocation via graph coloration

-

43:00

43:00

three address code, dags, basic blocks and flow graphs | important problems

-

22:05

22:05

compiler design module 85 : register allocation

-

4:47

4:47

gate cs 2013,q49: what is the minimum number of registers needed in the instruction set architecture

-

9:46

9:46

coloring code: how compilers use graph theory

-

57:03

57:03

mod-09 lec-30 global register allocation - 3

-

20:01

20:01

16 register allocation

-

31:52

31:52

live: interactive problem solving session on compiler design

-

4:22

4:22

gate cs 2014 set 1 | question: 3 let g = (v , e) be a directed graph where v is the set of vertices