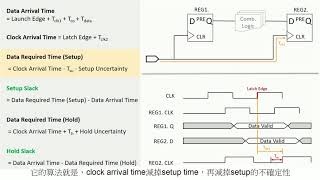

clock and input output delay constraints in quartus timings analyzer

Published 2 years ago • 4.3K plays • Length 9:03Download video MP4

Download video MP3

Similar videos

-

6:11

6:11

calculating correct timing data for compilation in quartus

-

34:39

34:39

timing analyzer: required sdc constraints

-

29:58

29:58

intel® quartus® prime pro software timing analysis – part 3: clock constraints

-

4:41

4:41

fpga timing analysis - peripheral constraints

-

14:00

14:00

how to fix timing errors in your fpga design during place and route, meeting clock constraints

-

3:36

3:36

using pll ip in quartus, to get high frequency clock

-

17:53

17:53

intel® quartus® prime pro software timing analysis – part 4: i/o interfaces

-

25:42

25:42

timing analyzer: intel® quartus® prime software integration & reporting

-

28:39

28:39

intel® quartus® prime pro software timing analysis – part 5: timing exceptions

-

27:27

27:27

intel® quartus® prime pro software timing analysis – part 1: timing analyzer

-

15:55

15:55

timing analyzer: introduction to timing analysis

-

16:34

16:34

fpga - 14, quartus: timequest timing analyzer

-

10:17

10:17

using signal tap analyzer in quartus, to monitor signals live on fpga

-

31:07

31:07

fpga timing optimization: quartus timing analyzer old

-

9:19

9:19

intel® quartus® prime pro software timing analysis – part 2: sdc collections

-

31:45

31:45

fpga timing optimization: quartus timing analyzer