clock divided by 3 with 75% duty cycle.

Published 4 years ago • 15K plays • Length 12:00Download video MP4

Download video MP3

Similar videos

-

![clock divided by 3 || explained step by step! [frequency divide by 3 ] f/3 or f/odd number](https://i.ytimg.com/vi/wxUqxSE_F5A/mqdefault.jpg) 21:06

21:06

clock divided by 3 || explained step by step! [frequency divide by 3 ] f/3 or f/odd number

-

6:48

6:48

how to design clock divided by 4.5 ? explained!

-

![[frequency divide by 2 ] clock divider explained!!](https://i.ytimg.com/vi/3zZ2y-0XzwQ/mqdefault.jpg) 5:16

5:16

[frequency divide by 2 ] clock divider explained!!

-

4:28

4:28

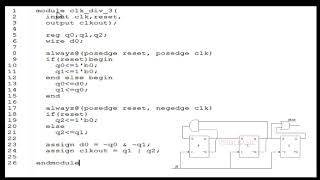

clock divider by 3 with duty cycle 50% using verilog

-

13:16

13:16

frequency divider circuit - divide by 3 | digital electronics

-

18:16

18:16

step by step method to design any clock frequency divider

-

9:00

9:00

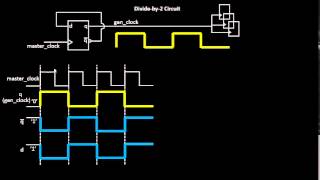

generated clock divide-by-2 circuit

-

8:53

8:53

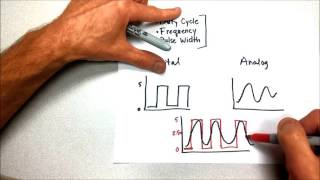

duty cycle, frequency and pulse width--an explanation

-

11:20

11:20

what is pulse width modulation ? | duty cycle, pulse width and frequency explained.

-

7:02

7:02

frequency multiplier - theory and prototyping example

-

2:34

2:34

divide clock frequency by 3 with 50% duty cycle by using a karnaugh map?

-

8:22

8:22

mod 5 counter with 70% duty cycle

-

1:18

1:18

designing a divide-by-5 counter with equal duty cycle: a technical guide

-

1:32

1:32

electronics: jk flip-flop as a frequency divider by 3 with a duty cycle of 50%

-

5:37

5:37

duty cycle, pulse width & frequency - rectangular and square waves

-

6:53

6:53

vlsi : clock divider verilog code and clock divider by 2 and frequency divider

-

0:28

0:28

25 khz clock with 25% duty cycle

-

5:56

5:56

clock frequency multiplier part 2

-

3:47

3:47

digital electronics - clock frequency division

-

0:14

0:14

design frequency divider circuit with ic74ls163