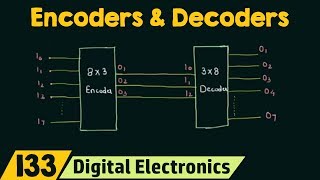

decoder in digital systems design

Published 5 years ago • 1.9K plays • Length 11:40Download video MP4

Download video MP3

Similar videos

-

8:16

8:16

4*16 decoder design using 2*4 decoder

-

8:31

8:31

encoder in digital systems design || encoder || encoder in digital electronics

-

9:16

9:16

q. 4.23: draw the logic diagram of 2-to-4-line decoder using (a) nor gates only (b) nand gates only

-

10:22

10:22

multiplexer in digital system design || multiplexer || digital electronics

-

4:53

4:53

binary decoder: what is it? (and how does it work) | electrical4u

-

12:05

12:05

4.10: design a four-bit combinational circuit 2’s complementer. (the output generates the 2’s

-

12:20

12:20

q. 4.8:design a code converter that converts a decimal digit from the 8, 4, –2, –1 code to bcd

-

11:55

11:55

demultiplexer in digital electronics

-

5:03

5:03

sequential logic in digital systems design

-

9:34

9:34

full subtractor in digital systems design

-

6:17

6:17

q. 4.26: construct a 4-to-16-line decoder with five 2-to-4-line decoders with enable.

-

8:53

8:53

q. 4.25: construct a 5-to-32-line decoder with four 3-to-8-line decoders with enable and a 2-to- 4

-

6:52

6:52

introduction to encoders and decoders

-

12:17

12:17

q. 7.15: using 64 * 8 rom chips with an enable input, construct a 512 * 8 rom with eight chips and a

-

14:15

14:15

bcd adder in digital systems design || truth table, k-map and circuit diagram

-

6:26

6:26

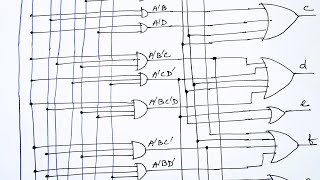

q. 4.28: implement a full adder with a decoder and nand gates. the adder inputs are a, b, and c.

-

6:33

6:33

q. 4.29: implement a full subtractor with a decoder and nand gate. the subtractor inputs are a, b, c

-

26:34

26:34

q. 4.9: an abcd-to-seven-segment decoder is a combinational circuit that converts a decimal digit in

-

12:27

12:27

q. 5.1: the d latch of fig. 5.6 is constructed with four nand gates and an inverter. consider the