electronics: verilog reset example within clock domain crossing example (2 solutions!!)

Published 2 years ago • 11 plays • Length 2:34Download video MP4

Download video MP3

Similar videos

-

1:51

1:51

electronics: asynchronous fifo in clock domain crossing

-

16:38

16:38

crossing clock domains in an fpga

-

8:33

8:33

3 bit up_counter @positive edge clock using #verilog #edaplayground #vlsi

-

11:31

11:31

reset synchronizer | reset synchronizer circuit | active high / low reset | vlsi interview questions

-

4:08

4:08

clock domain crossing issues|| system verilog concepts|| let us learn

-

13:23

13:23

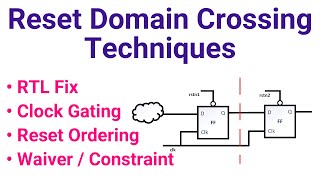

reset domain crossing technique | rdc technique | how to fix rdc violation | vlsi interview question

-

12:05

12:05

synchronous reset and asynchronous reset | synchronous reset vs asynchronous reset | what is reset?

-

11:07

11:07

vlsi : synchronous reset vs asynchronous reset active low

-

7:04

7:04

reset domain crossing (rdc) basics | reset recovery | reset removal | rdc basics | vlsi interview

-

14:00

14:00

how to fix timing errors in your fpga design during place and route, meeting clock constraints

-

23:56

23:56

asynchronous fifo | clock domain crossing (cdc) | fifo rtl design

-

6:01

6:01

synchronous reset asynchronous reset in sequential design with verilog code

-

1:31

1:31

electronics: clock domain crossing of a bus between related clocks

-

5:56

5:56

metastability |clock domain crossing(cdc) with respect to reset | reset crossing

-

12:28

12:28

synchronous & asynchronous reset part-1 #verilog @edaplayground #synchronous #reset

-

9:53

9:53

⨘ } vlsi } 24 } reset domain crossings, solutions } le profofesseur }

-

0:37

0:37

how much does a chipset engineer make?

-

23:08

23:08

module 6.1 logical clocks