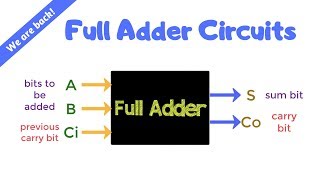

full adder in digital logic design

Published 5 years ago • 1.8K plays • Length 13:36

Download video MP4

Download video MP3

Similar videos

-

26:34

26:34

q. 4.9: an abcd-to-seven-segment decoder is a combinational circuit that converts a decimal digit in

-

50:14

50:14

tutorial 1: half adder circuit design using matlab hdl coder - part (1)

-

6:06

6:06

full adder.avi

-

6:26

6:26

q. 4.28: implement a full adder with a decoder and nand gates. the adder inputs are a, b, and c.

-

5:57

5:57

half adder || truth table, k-map and circuit diagram

-

14:15

14:15

bcd adder in digital systems design || truth table, k-map and circuit diagram

-

9:35

9:35

q. 4.17: show that the output carry in a full adder circuit can be expressed in and-or-invert form

-

5:48

5:48

q. 4.35: implement a full adder with two 4 * 1 multiplexers.

-

8:45

8:45

q. 5.7: a sequential circuit has one flip-flop q, two inputs x and y, and one output s. it consists

-

8:01

8:01

q. 3.29: implement the following four boolean expressions with three half adders: d=a⊕b⊕c

-

22:22

22:22

q. 6.9: two ways for implementing a serial adder (a b) is shown in section 6.2. it is necessary

-

5:53

5:53

half subtractor in digital systems design || truth table, k-map, and circuit diagram

-

6:33

6:33

q. 4.29: implement a full subtractor with a decoder and nand gate. the subtractor inputs are a, b, c

-

12:47

12:47

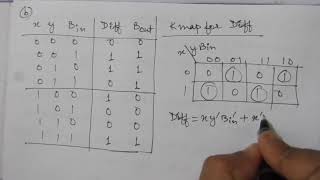

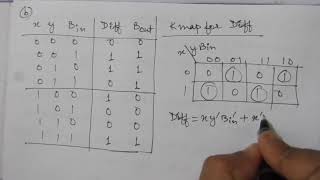

q. 4.12: (a)design a half-subtractor circuit with inputs x and y and outputs diff and bout. the circ

-

6:35

6:35

q. 6.8: the serial adder of fig. 6.6 uses two four‐bit registers. register a holds the binary number

-

3:47

3:47

full adder explained: binary addition simplified in under 5 minutes | digital electronics ep 19

Clip.africa.com - Privacy-policy

26:34

26:34

50:14

50:14

6:06

6:06

6:26

6:26

5:57

5:57

14:15

14:15

9:35

9:35

5:48

5:48

8:45

8:45

8:01

8:01

22:22

22:22

5:53

5:53

6:33

6:33

12:47

12:47

6:35

6:35

3:47

3:47