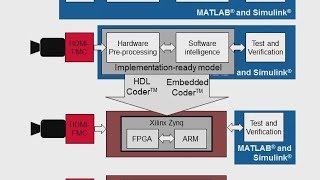

vision processing for fpga, part 4: targeting a lane detection design to a xilinx zynq device

Published 5 years ago • 2.4K plays • Length 4:59Download video MP4

Download video MP3

Similar videos

-

5:04

5:04

vision processing for fpga part 5 hardware software prototyping of a lane detection design

-

5:23

5:23

vision processing for fpga, part 3: hardware design of a lane detection algorithm

-

4:43

4:43

getting started using xilinx zynq with computer vision system toolbox

-

5:37

5:37

targeting a corner detection design to fpga hardware

-

40:01

40:01

bridging analog and digital worlds at high speed with the jesd204 serial interface

-

27:58

27:58

implementation of gpio via mio and emio in all programmable soc zynq 7000

-

2:36

2:36

real-time video processing on zybo fpga

-

5:44

5:44

designing a datapath from an fpga to a processor with soc blockset: xilinx deployment

-

14:19

14:19

fpga vision - circuit design

-

5:16

5:16

vision processing for fpga, part 1: vision processing fpga and asic hardware considerations

-

9:59

9:59

fpga vision - lane detection

-

5:08

5:08

vision processing for fpga, part 2: from a frame-based algorithm to a pixel-streaming implementation

-

5:41

5:41

matlab as axi master with xilinx fpga and zynq soc boards